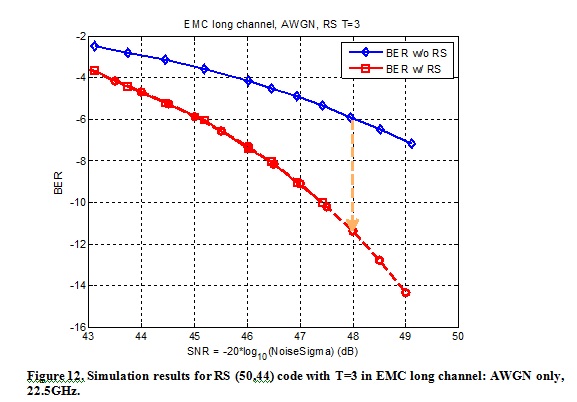

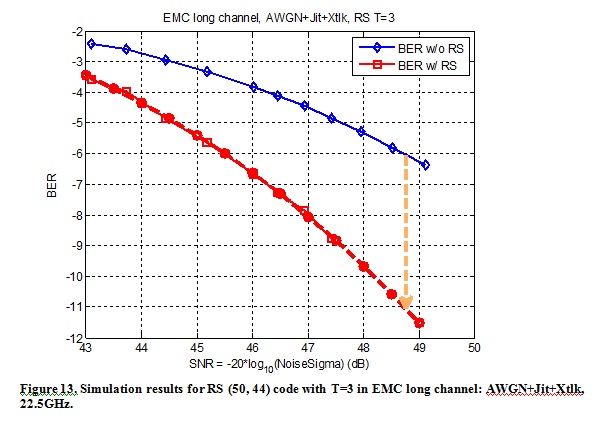

Figure 14 and Figure 15 show the simulation results of RS(52,44) in EMC long channel with different noise properties. Figure 13 is for EMC long channel with AWGN only, where 1e-6 raw BER can achieve 5e-18 after FEC BER. Figure 14 is for EMC long channel with AWGN+Jit+Xtlk combined noise, where 1e-6 raw BER can achieve 5e-17 after FEC BER.

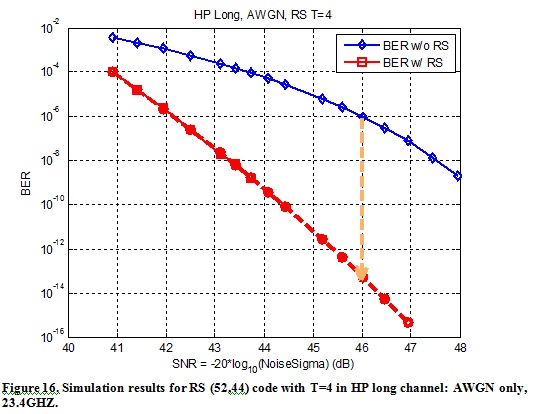

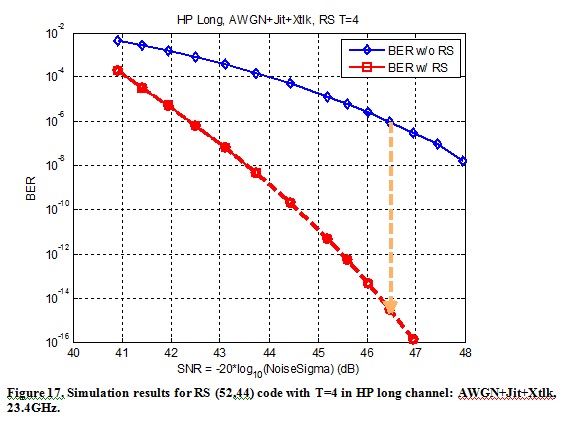

Figure 16 and Figure 17 show the simulation results of RS(52,44) in HP long channel with different noise properties. Figure 15 is for HP long channel with AWGN only, where 1e-6 raw BER can achieve 5e-14 after FEC BER. Figure 16 is for HP long channel with AWGN+Jit+Xtlk combined noise, where 1e-6 raw BER can achieve 4e-15 after FEC BER.

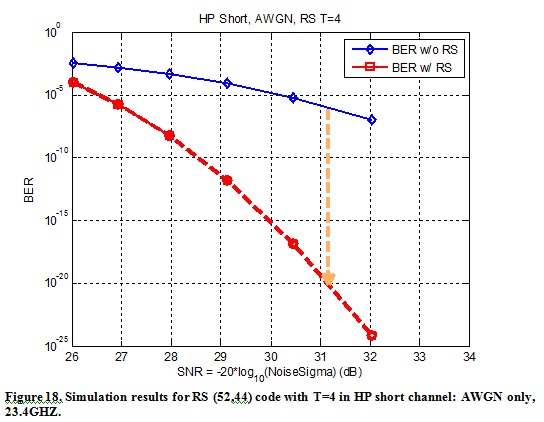

Figure 18 and Figure 19 show the simulation results of RS(52,44) in HP short channel with different noise properties. Figure 17 is for HP short channel with AWGN only, where 1e-6 raw BER can achieve 1e-20 after FEC BER. Figure 18 is for HP short channel with AWGN+Jit+Xtlk combined noise, where 1e-6 raw BER can achieve 4e-20 after FEC BER.

Conclusions

The study in this paper shows that a strong FEC code such as RS(52,44) with error correction capability T=4 can be used in order to achieve after FEC BER around 1e-15 with raw BER = 1e-6. If strong FEC codes are not an option because of implementation complexity, then an interleaving scheme can be used to serve the purpose. With the channels we have simulated, it looks like three-way interleaving performance is very close to two-way interleaving of SAS4 FEC codes.

As data rates go higher with insertion loss becoming bigger, we strongly believe that current 128b/130b encoding is not a good option as the two-bit 01/10 overhead suffers due to its Nyquist pattern property.

An earlier version of this paper was a DesignCon 2018 Best Paper Award Winner.

Download the entire paper as PDF

References

[1] SAS4 standard sas4r06, Working draft American National Standard, Project T10/BSR INCITS 534, revision 06, 11 May 2016.

[2]S. Safwat et. al, “A 12Gbps All Digital Low Power SerDes Transceiver For on-chip Networking,” IEEE International

Symposium on Circuits and System (ISCAS), pp. 1419-1422, Rio de Janeiro, Brazil, May 2011.

[3] V. Balan et. al, "A 15–22 Gbps Serial Link in 28 nm CMOS With Direct DFE", IEEE Journal of Solid State Circuits, vol. 49, no. 12, Dec. 2014.

[4] R. Narasimha et. al, “Design of energy-efficient high-speed links via forward error correction,” IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 57, no. 5, pp. 359–363, May 2010.

[5] S. Kiran et. al, "A single parity check forward error correction method for high speed I/O", Signal and Information Processing (GlobalSIP) 2014 IEEE Global Conference on, pp. 652-655, 2014.

[6] S. B. Wicker (Editor) and V. K. Bhargava (Editor), "Reed-Solomon Codes and Their Applications", IEEE Press, 1994.

[7] J. Shehzad et. al, "FPGA Implementation of Reed-Solomon Code", Lambert Academic Publishing, 2015.

[8] S. Karve, "Reed-Solomon Codes: Theory and Techniques", Lambert Academic Publishing, 2017.

[9] H. Xia et. al, “Application of soft-decision Reed-Solomon decoding to magnetic recording systems” IEEE Trans. Magnetics, vol. 40, no. 5, pp.3419-3430, Sept. 2004.

[10] H. Xia et. al, “Reliability-based forward recursive algorithms for algebraic soft-decision decoding of Reed-Solomon codes”, IEEE Trans. Communications, vol. 55, no. 7, pp. 1273-1278, July 2007.

Author(s) Biography

Haitao (Tony) Xia is Distinguished Engineer of R&D at Broadcom Ltd, leading the research and development of advanced read channel and Serdes architectures for data storage systems. Dr. Xia served as Chairman of IEEE Data Storage Technical Committee and President of Chinese American Information Storage Society (CAISS) in the past. Before his work at Broadcom/Avago/LSI, Dr. Xia worked at Silicon Valley start-up, Linked-A-Media Devices, on signal processing and coding in the area of magnetic recording channels and non-volatile memories. Dr. Xia has published more than 20 articles in peer-reviewed journals/conferences, and has more than 120 US patent granted to his name. Dr. Xia is an IEEE Senior Member.

Haotian Zhang is a Principal Engineer of R&D at Broadcom Ltd in Longmont, CO., working on the research and development of advanced read channel and Serdes architectures for data storage systems. He holds PhD (2005) degree in electrical and computer engineering from Carnegie Mellon University, Pittsburgh, PA, and MS (2000) and BS (1997) degrees in electrical engineering from Tsinghua University, Beijing, China. Before his work at Broadcom/Avago/LSI, Dr. Zhang worked at Marvell and Maxtor on signal processing in the area of magnetic recording channels and optical channels..

Aravind Nayak is a Principal Engineer with Broadcom Ltd in Allentown, PA. He holds PhD (2004) and MS (2000) degrees in electrical engineering from the Georgia Institute of Technology, Atlanta, GA, and B. Tech (1999) degree in electrical engineering from the Indian Institute of Technology, Madras, India. His research interest include signal processing for the magnetic recording read channel and SerDes applications.

Bruce Wilson is Director of Architecture at Broadcom's Data Controller Division and worked to advance signal processing and electronics for Data Storage for more than 20 years. Bruce received his Doctorate at Stanford University and has worked at IBM, HGST, LSI and Broadcom.

Jun Yao is currently at Etopus, a Silicon Valley startup to make fast connections. Dr. Yao worked at Broadcom as Senior Engineer and Postdoctoral Researcher at Carnegie Mellon University, PA. He obtained his PhD degree (2013) in electrical and electronic engineering from Nanyang Technological University, Singapore, and bachelor degree (2008) from Harbin Institute of Technology, China. His research interests include signal processing, equalization, phase-locked loop, detection and decoding algorithms for the hard disk drive (HDD) read channel and high-speed Serializer/Deserializer (SerDes) communications.