Any discontinuity in a printed circuit board communication channel has the potential to significantly distort the signal propagating through it. This difficult-to-equalize distortion eats into loss budgets, ultimately reducing channel reach. Analyzing and optimizing each potential discontinuity has resultantly become a critical component of board-level signal integrity: particularly for very long channels that push the loss capabilities of the devices they connect.

Vias can become particularly painful to optimize as bandwidth increases: largely due to the increased influence of their barrels. The varying barrel length (dependent on layer-pair) can detune a structure that appeared to work acceptably for the layer pair simulated during its design. Designers can easily get trapped in a cycle of iterating over and over as they try to find a structure that works for every layer.

It is therefore attractive to look inside variable length structures like vias to confidently understand how they are tuned, and not just if they are tuned for a given length. For example, a designer may seek to match each ‘part’ of a via to the characteristic impedance in such a way that the performance is not length dependent: exactly like impedance matching long transmission lines. The typical TDR-centric design approach that iterates on the whole structure is not well suited to this task, however. The displayed values are dependent on loss, rise time, multiple interacting reflections, windowing, etc—all crippling the ability to accurately look inside a structure.

Two classic concepts can be leveraged to solve this problem: decomposing structures into separate models during iteration, and applying image impedance as a precisely defined and frequency-dependent analog to characteristic impedance. Both concepts are discussed in this summary, along with a simple tuning strategy that takes advantage of both components to accelerate an example eight signal-layer via design. The nominal example design achieves 25 dB return loss for every microstrip to strip line transition, and at almost half the simulation time estimated for the traditional TDR-centric method.

Decomposition

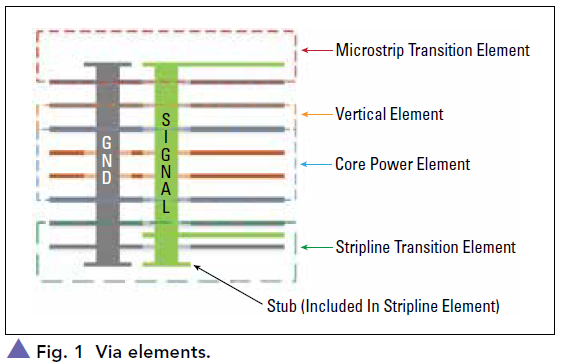

The first fundamental concept is decomposition: breaking the structure into logical components that are analyzed separately during iteration. Though via decomposition is a well-established concept, it has typically been used for modelling purposes—not design. [1, 2] When decomposition has been used for design, it’s often to study phenomenon well above current widely-adopted SerDes data rates. [3, 4] In this paper, surface to inner-layer vias are decomposed into four elements: the microstrip transition, a single cell of the periodic ground-signal-ground vertical geometry (referred to here as the “vertical element’), any power-layer crossing, and the stripline transition with stub. (See Figure 1)

Each element is then modelled separately in a fullwave solver—in this case the ANSYS HFSS 3D FEM field solver. TEM wave ports are placed at every element boundary, with launches created by extending the external faces of each element. The wave ports are fully de-embedded from the results after solving (See Figure 2).

Wave ports are used to eliminate fringe field artifacts that can appear with other types of ports and simulations. The boundaries of each element are chosen based on the assumption that the field structure in the actual structure is dominantly TEM at those locations. The degree to which this is not true will degrade accuracy—particularly if there is any significant field interaction between elements in the full structure.

The launches are kept deliberately short to minimize their influence on convergence during meshing. A relatively strict ΔS convergence criteria of 0.005 is used as well, due to the very small physical size of each structure.

Note that many other decomposed modeling techniques have been demonstrated in the past. The full paper also discusses a 2D method similar to some of those existing techniques: trading some accuracy for the ability to solve only once per cross-section geometry, with no need to re-solve for most material changes.

Image Impedance

The second fundamental concept that can enable easily looking inside structures to understand and control how they are tuned is an additional figure-of-merit. Return loss may be familiar, but is not meaningful for a single section of a periodic or varying length structure like via barrels. For this reason, a precisely defined and frequency-dependent analog to characteristic impedance is especially desirable for these elements: something that is not dependent on length, and that indicates a reflection-free structure when equal to the terminating impedance. We find exactly that in a property known as “image impedance.”

Image impedance is a two-port network property used in classic filter-design techniques dating back to the 1930s. [5] The image impedance of each port in an arbitrary two port network is defined as that port’s input impedance when the opposite port is terminated in its own image impedance [5], as shown in Figure 3.

Image Impedance can be calculated in terms of Z parameters– a common output of field solvers–as:

An image impedance can also be easily defined for each mode of a multi-conductor structure’s ports so long as there is no mode conversion–effectively treating each mode as an isolated two port network. This is exploited in the example design presented at the end of this paper to define a differential-mode image impedance.

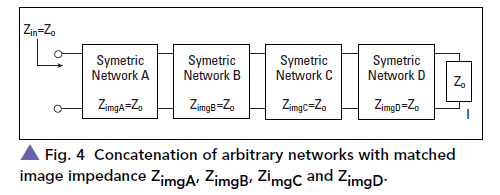

Symmetric networks conveniently jave identical image impedances for both ports. [5] An arbitrary number of symmetric networks with identical image impedances, Zimg [2] can therefore be cascaded while always presenting an input impedance of Zimg as long as the output termination is also matched to Zimg (See Figure 4).

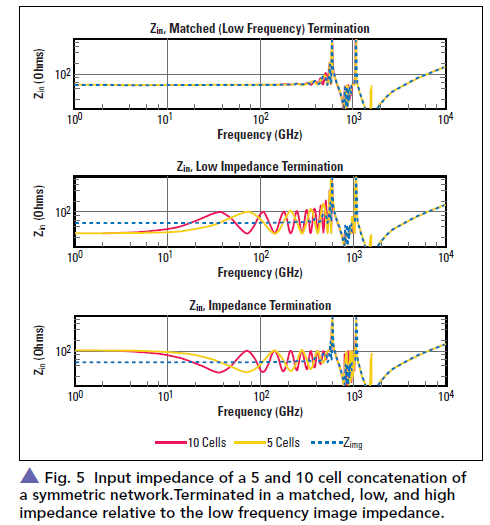

The full paper runs through several examples informally demonstrating some properties of image impedance and drawing parallels to characteristic impedance. Ultimately, a symmetric circuit with a known image impedance is concatenated five and ten times, each concatenation is terminated with a matched, high, and low impedance, and the input impedance of each concatenation is examined: (See Figure 5)

This example informally demonstrates two parallels to the behavior of a varying length transmission line with Z0=Zimg:

1. The image impedance of a concatenation of one symmetric circuit is not dependent on how many times it is concatenated: the final image impedance is the same as the image impedance of the base circuit. Similarly, transmission line characteristic impedance does not change with length.

2. The input impedance oscillates about the image impedance when mis-terminated. The period of this oscillation gets shorter as more cells are concatenated. Similarly, the input impedance of a lossless transmission line oscillates about the characteristic impedance when mis-terminated, with the period dependent on length. This is crucial to keep in mind during design—length matters if every single element is not precisely matched.

Full periodic structure theory can be used to more rigorously explain the demonstrated behavior. It is possible to define a propagation constant for periodic structures, along with a more rigorous analogy to Zo—Bloch Impedance. Image impedance is used here, however, due to its intuitive link to impedance matching. Also note that image impedance simplifies to Bloch impedance for networks that are both symmetric and reciprocal. (Look up the definitions in [5] and try it yourself!)

Example Tuning Strategy and Design

The paper closes with an example design that leverages decomposition and image impedance to accelerate the design of an 8 signal-layer midplane via with better than 25 dB return loss for every single microstrip-stripline transition. A simple tuning strategy is defined as part of the example, based on the assumption that the stub will be the hardest element to tune. The simple strategy demonstrates the practical application of decomposition and image impedance, even without rigorous tuning theory. The design targets for each element are:

- Stripline transition plus stub: the minimum return loss allowed for the entire structure: higher if possible. Note that using the absolute minimum will only work over a finite bandwidth unless the other elements are perfectly matched.

- Vertical element: image impedance as close to the nominal terminating impedance as possible, calculated with Eq. (1) or (2). Both give the same result due to the symmetry of the vertical element.

- Microstrip transition: 10 dB higher return loss than the minimum: chosen arbitrarily based on the assumption that it is high enough to not meaningfully degrade the structure’s performance.

- Core: 10 dB higher return loss than the minimum, chosen for identical reasons as the microstrip target.

In the example design, each element of the via was iterated to achieve the above targets. Notably, tuning the stub without cumbersome-to-implement geometry required an antipad structure that gave a higher than optimal vertical-element image impedance. To predict how this would impact performance, the relevant solution of the vertical element was concatenated with the stub solution a variable number of times— recalling that length matters unless perfectly matched and terminated. The results predicted acceptable performance, so the design continued with the adjusted antipad.

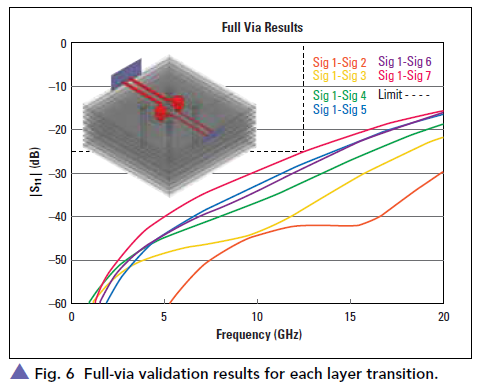

After each element was optimized, the complete structure was solved to verify that the performance targets had been met for every layer transition.This full simulation showed a successful design, with greater than 25 dB return loss for every microstrip to stripline layer transition (See Figure 6).

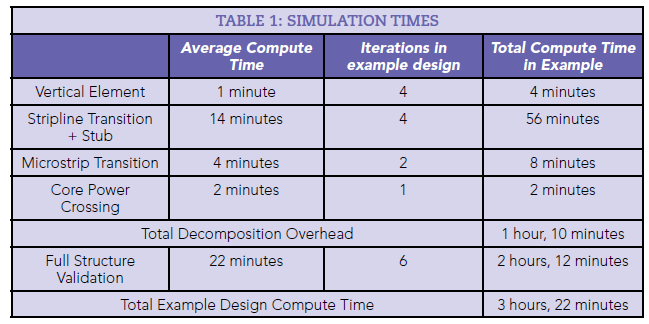

Furthermore, the example design only required 3 hours and 22 minutes of total simulation time, including validation of the full structure for each layer pair (See Table 1).

A traditional full-structure iterative approach might take an experienced engineer three iterations per layer transition. At an average compute time of 22 minutes per full-via solve, this gives a design time of 6 hours and 36 minutes.The decomposition technique is almost twice as fast. To break even with this technique, a designer would be allowed just four iterations to converge to a solution for a single layer transition that then works across the five other transitions with no further iteration after validation.

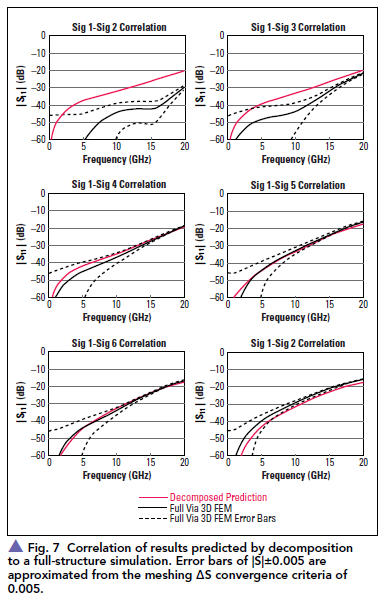

Correlation

The results predicted by decomposition are shown in the full paper to correlate very well with the solved complete-via for all but very short vias (See Figure 7). This discrepancy may be caused by field interaction between internal and surface pads that occur only for short vias, and cannot be captured by decomposition.

Conclusions

Decomposition and image impedance can accelerate and improve design by allowing designers to confidently look inside structures and interpret the results with an intuitive figure-of-merit. This enables spatially aware tuning strategies and design techniques, such as the example demonstrated in this paper.

Furthermore, tuning techniques need not focus on matching each element, as was the focus in this paper—high impedance elements can be used to easily tune low impedance elements over limited bandwidths. More advanced techniques are possible as well.

The ability to understand how a structure is tuned (or mis-tuned) is extremely powerful, and allows designers to identify and iterate on problematic areas with full confidence. Looking forward, techniques like decomposition that improve on traditional design flows will only become more useful as industry trends toward 56G PAM4 and considers 56G NRZ and higher.

This paper was presented at DesignCon 2017. Download entire paper here.

References

[1] G. Antonini et al., “Equivalent Network Synthesis for Via Holes Discontinuities,” IEEE Adv. Packag., vol. 25, no. 4, pp. 528-536, Nov. 2002

[2] E. Laermans et al., “Modeling Complex Via Hole Structures,” IEEE Adv. Packag., vol. 25, no. 2, pp. 206-214, May 2002

[3] X. Duan et al., “Optimization of Microstrip-to-Via Transition for High-Speed Differential Signaling on Printed Circuit Boards by Suppression of the Parasitic Modes in Shared Antipads,” in IEEE Int. Symp. on Electromagnetic Compatibility, Aug. 2014

[4] C. Tsai et al., “Design of Microstrip-to-Microstrip Via Transition in Multilayered LTCC for Frequencies up to 67 GHz,” IEEE Trans. Compon. Packag. Manuf. Technol., vol. 1, no. 4, pp. 595-601, April 2011

[5] D. M. Pozar, “Microwave Filters,” in Microwave Engineering, 4th ed. New York: Wiley, 2012, ch. 8, sec. 8.2, pp. 388-390