So what? This question should be asked more often. It’s one thing to notice an effect, it’s another thing to have this effect cause a problem. This is especially true if it may cost money to fix the problem. Is it worth it?

So there is some noise on the power rail on a die. So what? What’s the downside of the noise?

When we evaluate a noise budget for the signals at receivers, we usually identify three noise sources: reflection noise, cross talk and power rail noise. In typical worst case noise budgets, we might have about 15% of the Vcc swing as the noise margin on one side. Without a strong negotiator for a particular noise source, we generally allocate the 15% margin equally amongst the three sources and give rail noise 5% of Vcc as the acceptable limit.

Some devices, like ADCs and DACs, are much more sensitive to voltage rail noise and can’t tolerate anything close to 5% noise. For these devices, the acceptable rail voltage noise is much less.

Voltage rail noise can also affect jitter. As high-speed serial link interconnects push the limits to physics and practical equalization techniques, jitter from all other sources need to be reduced. This is another reason why rail noise on die should be reduced even lower than this 5% limit.

When the Vdd is higher than nominal, charge carriers in the transistors’ channels see a higher electric field, drift through the channel in a shorter time and the propagation delay of any gates tied to this rail is shorter. When Vdd is slightly lower than nominal, the electric field is lower, and the propagation delay is longer. This means that voltage noise on a Vdd rail will cause edges to pull in and push out. This is the very definition of jitter.

If this rail noise is on a device on which its jitter contributes to data jitter, such as a PLL, a spread spectrum clock source, any clock data recovery circuitry or even on any transmitter circuits, Vdd rail noise will add to the very tight jitter budget. In such a case, the allowable voltage rail noise might be less than the typical 5% value.

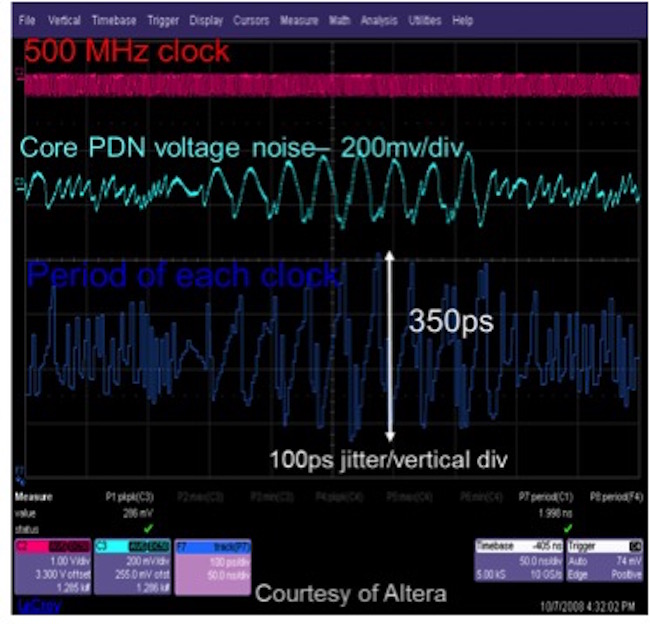

A beautiful example of this effect is shown in Figure 1.

Figure 1: Measured voltage noise and noise driven jitter on a test die.

A special test die was constructed with a clock distribution network that shared the power rail with a number of programmable gates. When these gates toggled, they drew considerable PDN current and, due to the impedance of the PDN, generated voltage noise on the rail. This voltage noise will push and pull the edges of the clock distribution gates.

On this special test die, the buffered clock signal was measured, the voltage noise on the die rail was measured, and the time interval error of the edges of the clock was measured. These three signals are displayed at the same time, in real time, in the figure above.

This measurement shows so clearly that as the voltage noise on the rail fluctuates due to many gates switching and drawing transient PDN current, the clock edge shows excess jitter. In this special test die, in this specific circuit, about 350 mV of rail noise created 350 psec of clock jitter.

This is yet another reason why the voltage rail on-die matters, a lot. Noise on the power rails will contribute to the voltage noise at the receiver adding to the noise margin, and in addition, contribute to jitter.

This is an important reason why reducing voltage rail noise is important, especially for devices that are sensitive to jitter.

For more information on this topic of where power rail noise comes from and how to reduce it, check out the recently released book Larry Smith and I wrote, Principles of Power Integrity for PDN Design- Simplified.

You can download a copy of the preface and chapter 1 by clicking on this link.