DesignCon 2018 will feature a 14-track conference covering the latest developments in hardware and high-speed communications design with over 100 technical sessions, three full day boot-camps, and more. DesignCon offers an in-depth, three-day conference program selected by the Technical Program Committee which is made up of more than 90 industry professionals. DesignCon's educational content covers all aspects of electronic design, including signal and power integrity; system co-design; and test and measurement methodologies. Here is a link to their conference overview.

In Nov, three new keynote presentations were announced covering NASA's New Horizons mission, the safety of autonomous vehicles and expert predictions of future challenges within engineering (panel session). Keynote speakers include Alice Bowman, Todd Hubing, Steve Sandler and Istvan Novak, from organizations such as Johns Hopkins University, Clemson University, Picotest, Oracle and more.

Signal Integrity Journal has collected the following exhibition highlights as a preview of some key hardware and software products you will see in the exhibition hall:

Visit Signal Integrity Journal at DesignCon in booth T1 for some great giveaways - see what we are giving away here.

American Standard Circuits - Booth 209

American Standard Circuits - Booth 209

American Standard Circuits (ASC) prides itself on being a total solutions provider, manufacturing quality rigid, metal-backed, RF/microwave, flex, and rigid-flex PCBs for the medical, automotive, industrial, defense, and aerospace markets in volumes from test and prototypes to large production orders. ASC has the expertise to provide a wide variety of technologies in a time-critical environment. Their qualifications include AS9100 Rev D, ISO 9001:2015, MIL-PRF 31032, MIL-PRF-55110, MIL-PRF-50884 certification and ITAR registration. American Standard also holds many key patents for metal bonding processes. For more information go to www.asc-i.com

ASC writes Design Guides Especially for Designers. For your free copy of "The Printed Circuit Designer’s Guide Fundamentals of RF/Microwave PCB’s" visit their booth.

Anritsu will demonstrate signal integrity solutions featuring its new Signal Quality Analyzer (SQA) MP1900A BERT, as well as VectorStar® and ShockLine™ vector network analyzers (VNAs). On Thursday, February 1, Anritsu will demonstrate standards-compliant 200G/400G PAM4 BER, jitter and noise tolerance testing of 56G PAM4 data signals, high-speed serial bus (PCIe 4.0, Thunderbolt™ and USB 3.0) receiver compliance tests, and 43.5 GHz and 70 GHz VNA signal integrity solutions in its booth and during technical sessions. Dr. Jon Martens will lead another technical discussion entitled Fixture De-embedding in Higher Crosstalk Situations on Wednesday, January 31.

ANSYS - Booth 747

ANSYS - Booth 747

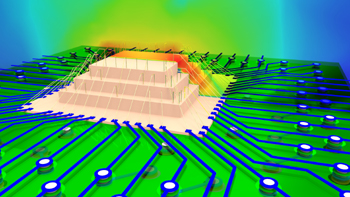

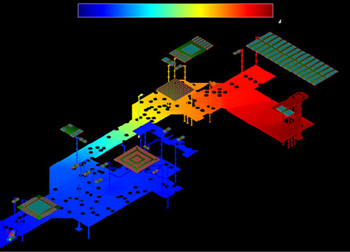

ANSYS will unveil new pervasive engineering solutions for Signal Integrity, Power Integrity and Electronics Reliability. Learn how our Chip-Package- System design flow can help you optimize your power and signal integrity designs and predict EMI. In addition, do not miss the opportunity to learn about our new integrated electro-thermal solution that delivers component and system level multi-physics analysis, automation, and robust design. Icepak is now integrated to the ANSYS Electronics Desktop alongside HFSS, Q3D Extractor and Maxwell enabling a smooth workflow with robustness for thermal analysis coupled to electromagnetics.

To learn more about ANSYS at DesignCon visit http://www.ansys.com/Other/designcon

Cadence - Booth 711

Cadence - Booth 711

Cadence will be demonstrating how you can optimize your signal and power integrity design for the latest DDR and serial link interfaces. A full summary of Cadence highlights at DesignCon, including technical sessions, panelists, and sponsored sessions are listed here – https://www.cadence.com/content/cadence-www/global/en_US/home/company/events/industry-events/designcon-2018.html.

Cadence booth demos will highlight:

- Constraint-driven power integrity design and analysis featuring easy setup with automated model and source/sink assignments

- Using patented simulation techniques to analyze equalization associated with high-speed DDR memory interfaces

- Multi-gigabit serial link design and analysis featuring compliance testing for popular interfaces such as PCI Express® (PCIe®) 4.0

- DDR-4400 IBIS-AMI model development

- Streamlining the flow between IC design and package/PCB design

Technical Sessions (conference pass) include:

- Reduction of Mode Conversion in SerDes Links

- Temperature- and Geometry-Dependent Analysis of High-Speed PCB Traces (Joint presentation with Cisco)

- Performance Analysis for Next-Generation PCIe Interface

- Backchannel Modeling and Simulation Using Recent Enhancements to the IBIS Standard

- IBIS-AMI for PCI Express Gen 4 (Joint presentation with IBM)

Sponsored Sessions and Panels (free to all attendees) include:

- Panel – Machine Learning Advances in Electronic Design

- Panel – The Impact of Machine Learning on Solution Space Analysis: Are Circuit and Channel Simulation Obsolete?

- Panel – IBIS-AMI: New Users, New Uses

- Temperature- and Geometry-Dependent Analysis of High-Speed PCB Traces

- DDR-4400 IP Model Development Using AMI Builder

- Advanced IC Packaging Trends and Their Impact on EDA Tools

- HSSO - Physical Structure Optimization for High-Speed Interconnects

- Brand-New Electrical and Thermal Co-Simulation Analysis

- A New Platform Power Integrity Design Approach with SPIM and UPIT

- Heterogeneous Integration – More than Moore

- Panel – Temperature and Bias-Dependent Passive Component Models

CST - Booth 641

CST - Booth 641

CST will showcase the recently released CST STUDIO SUITE® 2018, which contains a number of tools to help engineers design, analyze and improve PCB layouts. The dedicated PCB simulation tools in CST STUDIO SUITE can be used to characterize the behavior of a layout quickly. CST STUDIO SUITE® also includes a rule-checking tool for PCB layouts, CST BOARDCHECK, which can automatically detect structures that may cause SI/PI or EMC problems. Layouts can be converted directly into a 3D model for full-wave simulation or into an equivalent circuit model for circuit simulation, with specialized meshing algorithms optimized for complex printed structures. IC designs can be imported through the CST chip interface, which mimics the real fabrication process to produce accurate simulation models. Learn more about CST’s solutions, visit our booth at DesignCon and visit https://www.cst.com/2018.

EMSCAN – Booth 211

EMSCAN – Booth 211

EMSCAN launches the EMxpert ERX. The world’s fastest high-resolution EMC/EMI scanner has been redesigned to operate with a high-performance external spectrum analyzer. Because of its unmatched fast speed and very intuitive GUI, the world’s fastest high-resolution EMC/EMI scanner has been the go-to EMC/EMI scanner for major semiconductor, IC and high-density PCB manufacturer and designers. Now, they can use the EMxpert ERX with their high-end external spectrum analyzers. EMSCAN’s EMxpert ERX provides eight levels of resolution (60 microns to 7.5 mm) enabling the PCB and design engineers to diagnose EMC/EMI problems between 150 kHz and 8 GHz. For more information, visit www.emscan.com.

evissaP - Booth 1335

evissaP - Booth 1335

evissaP will be featuring the Max Bend eP formable cable series offers users the benefit of eP-Formable cable and the ability to reliably bend the cable at the cable-to-connector body interface. In many instances, formable cable can replace the need of expensive cable assemblies having precision right angle connectors operating to 18 and 26.5 GHz. The Max Bend eP-Formable cable series is truly a reliable, universal cable assembly for plumbing inside the box, outside the box and for use in test applications. You can hand form the Max Bend eP-Formable cable assemblies to final shape with ease.

Visit their web site for more information www.evissap.com.

ITEQ Corporation - Booth #1338

ITEQ Corporation - Booth #1338

ITEQ Corporation’s new halogen-free IT-88GMW is for use in 76-81 GHz automotive radar systems, emerging millimeter wave, and 5G base station applications. The product has a Dk of 3.00 and Df of 0.0012 at 10 GHz, making it the lowest loss product in the thermoset products category. IT-88GMW will be available in copper-clad laminate and prepreg and can be used in hybrid applications with standard FR-4 for use in automotive driver-assist systems as well as enabling high layer count boards for both daughter card and backplane applications.

Keysight – Booth 725

Keysight – Booth 725

Keysight will demonstrate the most advanced design and test solutions for solving today’s most difficult high-speed digital measurement challenges. Key focus will be on technologies moving to next Gen standards. In addition to the latest real-time and sampling oscilloscopes, BERTS, and logic analyzers, Keysight will feature software such as PAM4 measurement apps (N1085A/N8836A), SI/PI simulation (ADS 2017), Data Analytics (N8844A), physical layer test (N1930B PLTS), and compliance test (N6462A DDR4/LPDDR4, N5990A PCIe). Keysight’s industry experts will also lead eight complimentary, educational workshop sessions on: Signal Integrity, Data Analytics, 400G, PAM4, Type-C, PCIe 5.0, Design & Simulation, DDR4/DDR5.

Marki Microwave booth 1347

Marki Microwave booth 1347

The DMX-64 is a high speed SiGe 1:2 demultiplexer (DEMUX) chip in a connectorized module. This broadband 1:2 deserializer converts a DC to 64 Gb/s input signal into two half rate output signals using a half rate clock. The DMX-64 can be operated single ended or differentially. The DMX-64 is suitable for laboratory testing and use in test equipment.

Please visit their website for a complete high speed data catalog: www.markimicrowave.com.

Mentor, A Siemens Business - Booth 943

Mentor, A Siemens Business - Booth 943

Among various technical presentations, the Mentor team will feature HyperLynx® DRC which provides fast, comprehensive electrical design verification to all PCB layout persons, hardware engineers, and SI/PI/EMC experts, regardless of their layout tool or level of expertise. HyperLynx DRC’s automated approach can be used iteratively, to identify design violations that lead to signal integrity, power integrity, and EMI/EMC issues, eliminating manual inspection and PCB cycle bottlenecks.

Visit their web site for more information: www.mentor.com.

Pico Technology - Booth 1052

Pico Technology - Booth 1052

Pico Technology will be demonstrating their recently released PicoVNA 106, a professional-grade vector network analyzer for RF, microwave and gigabit data applications. With a frequency range of 300 kHz to 6 GHz, over 118 dB dynamic range, only 0.005 dB RMS trace noise at 140 kHz bandwidth, and "Quad RX" four-receiver architecture, it delivers unprecedented portability and cost efficiency. See the VNA 106 gather a 500-point 2-port .s2p Touchstone file in less than one tenth of a second. Observe the calibration process with the Pico SOLT (short, open, load and thru), 4-piece, 5-port low-cost calibration kit.

Remcom - Booth 207

Remcom - Booth 207

Remcom will demonstrate the latest release of XFdtd, featuring circuit co-simulation and expanded signal integrity capabilities. XF combines a time-domain circuit solver with its full wave electromagnetic solver and uses co-simulation to update complex circuit structures at each timestep in an FDTD simulation. Circuit co-simulation facilitates a more realistic analysis of device performance by including imported circuit components within the EM simulation. Now, users can import the schematic for a desired component via a netlist file, with support for SPICE elements such as resistors, capacitors, inductors, coupled inductors, and sub-circuits.

Rogers Corporation - Booth #421

Rogers Corporation - Booth #421

Rogers’ Research Fellow Al F. Horn III will unveil the results of research on how different circuit materials affect the performance of high-frequency analog or high-speed digital transmission lines, in his talk “Effect of Conductor Profile on the Impedance and Capacitance of Transmission Lines,” Wednesday, January 31 in Ballroom C, from 11:00 to 11:45am.

For the exhibition, Rogers’ will feature various circuit materials, with an emphasis on XtremeSpeed™ RO1200™ and RO4835™ laminates. XtremeSpeed RO1200 circuit materials are engineered to meet the unique electrical and thermal/mechanical demands of high speed designs. With a low dielectric constant of 3.05, and a maximum dissipation factor of 0.0017 @10 GHz, these laminates provide outstanding signal integrity, reduced signal skew, and reduced cross-talk. RO4835 laminates extend Rogers’ portfolio of high performance materials by providing customers with a match to the industry’s most used high frequency material, RO4350B™ laminates. The material processes similar to FR-4, is automated assembly compatible due to a low z-axis CTE and high Tg, and RO4835 laminates behave very similar to RO4350B materials through lead-free soldering temperatures.

R&S - Booth 521

R&S - Booth 521

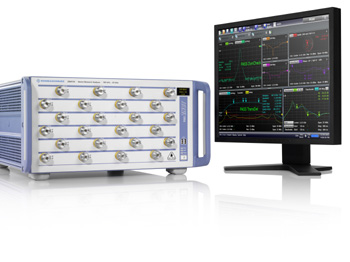

Rohde & Schwarz will feature their latest VNA, phase noise analyzer and oscilloscope solutions for signal integrity measurements. These solutions cover applications including high frequency multiport crosstalk (the first multiport vector network analyzer offering up to 24 integrated test ports), PAM-4, PCIe clock jitter, de-embedding and high speed PCB probing. Solutions, including power rail probes, will also be in the booth displaying power integrity measurements. Rohde & Schwarz will also be running a series of seminars on de-embedding, power integrity, clock jitter measurements, characterization of signal integrity using VNA’s and crosstalk (Jan 31, Great America 2).

Samtec- booth 841

Samtec- booth 841

Samtec will showcase several new high speed, high bandwidth products, including:

NovaRay™ is an innovative pin-to-ground differential pair configuration interconnect system that enables very low crosstalk to 40 GHz+, tight impedance control, and minimal variance in data rate as stack heights increase. The system is 112 PAM4 capable and is rated up to 56 Gbps NRZ per channel. It boasts an industry-leading aggregate average data rate of 1.33 Tbps per square inch. Right angle and vertical cable options are in development, which will combine NovaRay with Samtec’s Eyespeed™ Twinax cable. Cable and board interconnects are intermateable. For more information go to www.samtec.com/novaray.

Samtec’s FQSFP-DD is the first product to take the flyover architecture concept to the QSFP-DD form factor. QSFP-DD pluggable modules support double the aggregate bandwidth of conventional QSFP modules by adding a second row of contacts which enable support for a 16 differential pair electrical interface. Systems designed for QSFP-DD modules will be backwards compatible with existing QSFP plug-in modules and provide increased flexibility for end users, network platform designers and integrators. Samtec’s Flyover QSFP Systems provide improved signal integrity and architectural flexibility by flying critical high-speed signals over lossy PCB materials and directly to the panel via ultra-low skew twinax cable. This is the FQSFP -DD series.

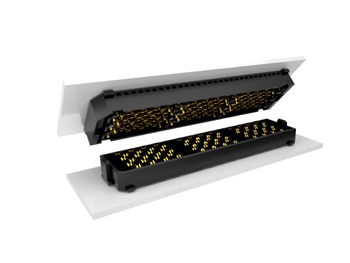

AcceleRate® HD is a .635 mm pitch, multi-row interconnect system that provides an ultra-high density interface and next generation bandwidth. The ADM6, ADF6 series has up to 240 total I/Os in a 1.88” square inches (12.1 square cm) of PCB real estate. This is possible because the interconnect’s four rows of pins, on .635 mm pitch, available in up to 60 pins per row, with a slim 5 mm wide insulator footprint. The mated stack height is a low 5 mm, with 7 mm and 10 mm stack heights to follow. The system is rated to 56 Gbps with PAM4 modulation.

Samtec’s new ExaMAX® Direct Mate Orthogonal (DMO) solutions offer system designers flexibility by removing the mid-plane, allowing fabric cards and line cards to mate directly. This fast-growing system architecture increases airflow and improves thermal efficiencies throughout the chassis. DMO solutions enhance signal integrity via shorter trace lengths and less connector transitions while streamlining the system BOM and optimizing system cost.

Click here for a complete listing of Samtec Presentations, Featured Events, Demos at DesignCon 2018.

Sierra Circuits – Booth 847

Sierra Circuits – Booth 847

Sierra Circuits has worked with over 20,000 engineers and PCB designers since 1986. We specialize in PCB manufacturing, assembly, high-density interconnect and high-speed technology. We handle all aspects of PCB production, and provide our customers with quality, reliability and a single point of support. Our goal is to work hand in hand with designers to help them get it right the first time, and save time and money.

Come talk with their experts at Booth #847 and get a free Design Guide to master controlled impedance, articles about high-speed PCB design, and fidget spinners!

Signal Microwave - Booth #1341

Signal Microwave - Booth #1341

Signal Microwave will be displaying 1 mm edge launch, board mounted connectors and test boards that operate mode free through 110 GHz. Test boards were developed in cooperation with Isola and based on their Astra material.

The plug and play de-embedding kit is highlighted in a paper being presented at DesignCon, “A NIST Traceable PCB Kit…”. The kit is to be used as a reference standard to evaluate de-embedding software and algorithms to a NIST traceable measured known device.

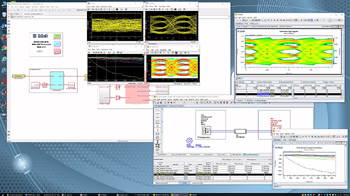

SiSoft – Booth 935

SiSoft – Booth 935

SiSoft’s AMI Modeling Bundle (AMB) integrates Quantum Channel Designer (QCD) and Quantum-SI (QSI) with Simulink and MATLAB, allowing designers to create AMI models in a systems context. Ready to run Tx/Rx examples for protocols like DDR5, CEI-56G and PCIe Gen3/4 are included. Examples use configurable building blocks, including a FIR filter, RX FFE, AGC, Peaking Filter, Saturating amplifier, DFE and CDR. Building blocks include MATLAB source code that designers can modify and extend, then generate AMI models directly from MATLAB without having to edit C code. Compiled models are then exported to QCD/QSI to verify compliance with the IBIS-AMI standard.

SiSoft is participating in the following activities:

Tuesday: Pragmatic Signal Integrity Boot Camp , 9 AM - 4:30 PM

Tutorial - Intro to IBIS-AMI, 1:30-4:30 PM

Todd Westerhoff - VP, Semiconductor Relations

Walter Katz - Chief Scientist

Location: Ballroom C

Wednesday: Building IBIS-AMI Models for DDR5 Applications, 11:05-11:45 AM

Todd Westerhoff - VP, Semiconductor Relations

Location: Mission City Ballroom M1

Panel - IBIS-AMI: New Users, New Uses, 3:45-5:00 PM

Location: Ballroom G

Thursday: Applying IBIS-AMI techniques to DDR4/5 analysis, 10:00-10:45 AM

Doug Burns - VP, Consulting, SiSoft

Eric Brock - Principal Member of Technical

Location: Ballroom B

Friday: DesignCon 2018 IBIS Summit Addressing DDR5 design challenges with IBIS-AMI modeling techniques

Todd Westerhoff - VP, Semiconductor Relations

Doug Burns - VP, Consulting

Eric Brock - Principal Member of Technical

Visit SiSoft at DesignCon and www.sisoft.com for more infomation.

Sonnet Software - Booth 311

Sonnet Software - Booth 311

Sonnet® Software will demonstrate their high frequency 3D planar EM analysis software, Sonnet Suites Version 16.54. With 30 years of experience, Sonnet utilizes the Shielded Domain Method of Moments technique to provide model extraction error frequently on the order of 1% or less. Sonnet offers high-accuracy analysis of predominantly planar (3D planar) circuits, interconnects in applications including RFIC, MMIC, and high density packaging applications, and handles kHz through THz frequencies. Sonnet Suites Release 16 features new integration with the Modelithics® CLR Library for Sonnet, speed increases in larger projects, and additional new features that give users more control and automation.

SV Microwave - Booth 702

SV Microwave - Booth 702

SV Microwave now offers edge mount solderless precision RF connectors in high frequency bands including the millimeter wave frequencies. These cost effective connectors are adjustable to accommodate multiple PCB thicknesses and use a solderless application for a fast and easy installation without damaging the PCB board. Their main applications include high speed digital component test, RF test and measurement boards, rapid prototyping, and military and aerospace. COTS versions are readily available through distribution.

Teledyne LeCroy - Booth 515

Booth demonstrations include:

- Integrated PCI Express® Gen3, Gen4, Gen5 test

- Digital Power Management and Power Integrity

- Automated PAM4 Eye and Jitter Analysis

- USB Type-C™ and Power Delivery Testing

- DDR compliance and debug capabilities

- HDMI and DisplayPort

Join Teledyne LeCroy for their technical presentations:

Keynote - SI/PI & EMI Challenges: Looking Ahead Through 2023

Eric Bogatin

Tue, Jan 30, 2018 12:00-12:45 pm | Mission City Ballroom

Tutorial – Principles of Power Integrity for PDN Design

Eric Bogatin

Tue, Jan 30, 2018 1:30 - 4:30 pm | Ballroom B

Panel - The Case of the Closing Eyes: Is PAM the Answer?

Martin Miller

Tue, Jan 30, 2018 4:45-6:00 pm | Ballroom E

The Gap Between Eye "Mask" Compliance, BER and BER Contours

Martin Miller

Wed, Jan 31, 2018 10:00-10:45 am | Ballroom A

PCIe Gen4 Compliance: From Physical to Protocol Layer

Patrick Connally, John Wiedemeier

Wed, Jan 31, 2018 2:00 - 2:40 pm | Mission City Ballroom M1

How To Keep Via To Via Coupling From Ruining Your Day

Eric Bogatin

Wed, Jan 31, 2018 4:30 - 5:15 pm | Chiphead Theater

A NIST Traceable PCB Kit For Evaluating The Accuracy Of De-Embedding Algorithms And Corresponding Metrics

Eric Bogatin

Thu, Feb 1, 2018 11:00-11:45 am | Ballroom G

The Protocol of the PHY: High-Speed Ethernet designs require protocol knowledge and awareness

David Rodgers

Thu, Feb 1, 2018 2:00 - 2:40 pm | Mission City Ballroom M1

PCI Express Gen3, Gen4 and Gen5 Physical Layer Test Requirements And Procedures

Patrick Connally

Thu, Feb 1, 2018 2:00-2:40 pm | GreatAmerica Meeting Room 2

Measuring Current and Current Sharing of DC-DC Converters

Peter Pupalaikis, Lawrence Jacobs

Thu, Feb 1, 2018 2:50-3:30 pm | Ballroom A

Secrets To Successful Power Rail Measurements

Eric Bogatin

Thu, Feb 1, 2018 3:30 - 4:15 pm | Chiphead Theater

Panel - 400G Test & Measurement Ready for the New Challenges Ahead

David Rodgers

Thu, Feb 1, 2018 3:45-5:00 pm | Ballroom C