It's time to plan your visit to DesignCon 2020 in Santa Clara! This year’s event takes place Tuesday, January 28 through Thursday, January 30 and is designated as the 25th anniversary event. (This is based on the timing of the first Design SuperCon, which was held in 1995 by HP, while that event actually grew out of road shows that began as early as 1989 [1].)

Attendees come to DesignCon to network, test out the latest products, and hear about what their peers have been working on for the last year. “For any engineer or technologist focused on high-speed communications, DesignCon is the center of the universe during the last week of January. Technology leaders in interconnect, silicon, EDA, test & measurement, power supplies, materials science, and other related industries (AI, 5G, IoT) use DesignCon as a platform for launching next-gen platform solutions,” observes Matt Burns, technical marketing manager, Samtec.

From the very beginnings of the earnest road shows of the late 1980s and early 1990s, DesignCon has been about signal integrity, and from there it grew to address power integrity. Now, the event is expanding its reach into other areas, such as 5G, automotive, and machine learning (introduced as a track in 2019), according to Suzanne Deffree, brand director, DesignCon, Informa Markets.

DesignCon 2020 is also welcoming an Informa partner from its DriveWorld event to support these new application areas. VSI Labs recently partnered with Informa during its Automated Drive West, an autonomous roadtrip from Minneapolis to Santa Clara for three engineers in VSI Labs’ research vehicle. At DesignCon, VSI Labs will share its firsthand knowledge on how autonomous technology reacts in different environments and conditions.

In addition to traditional technical content, this year’s event is planning career-focused sessions with experts on opportunities and challenges, mentorship, entrepreneurship, as well as resume and interview skills. A new Start-Up Zone will be added to the expo hall as well, featuring companies and entrepreneurs.

Deffree also reports that special events are planned around the 25th anniversary, including a champagne toast in the Chiphead Theater on Wednesday, January 29. Other networking opportunities will include networking lunches to All-Access Passholders, Booth Bar Crawls on the expo floor for all attendees, and the opening night party with a 1990s theme. Alumni, speakers, and technical program committee members can also catch up in the Chiphead Clubhouse.

On the expo floor, a networking lounge will offer all attendees and exhibitors a space to relax, regroup, and connect with their peers. DesignCon will also feature high-profile speakers in this lounge.

While the expo floor is fun and engaging, the technical conference is arguably the heart of DesignCon. And, its direction is influenced by the wisdom of the event’s respected technical program committee. This year’s event will include 14 reorganized tracks that aim to provide targeted information for engineers working across various applications.

According to the conference managers, the track with the most papers this year is “Signal & Power Integrity for Single-Multi Die, Interposer & Packaging,” known as Track 1. This is a change from previous years, when the tracks “Optimizing High-Speed Serial Design” and “Modeling & Analysis of Interconnects” hosted the most papers. The conference organizers have noted a growing interest in foundational design concepts, and Track 1 papers tend to define signal integrity and power integrity issues at the chip level, which could appeal to engineers who are in the early stages of their career as well as those more experienced who are expanding into other areas.

The conference program is rounded out with panels, in-depth trainings, and keynote talks. “DesignCon has evolved over the years to become an all-inclusive event for all things in the SI/PI world,” says Wally Arceneaux, technical marketing manager, Rohde & Schwarz USA Inc. “Not just papers anymore, but also bootcamps, panels, and networking events. With ever increasing data rates, there are always new challenges that push design engineers to require better tools.”

DesignCon also takes the time to recognize excellence, offering awards ceremonies before the keynote session on Wednesday, January 29 and Thursday, January 30. The DesignCon Engineer of the Year award recognizes an engineer who has demonstrated excellence in chip, board, or systems leadership, creativity, and design, with particular attention to signal and power integrity. Each year the event also hosts its Best Paper Awards, acknowledging the current year’s finalists and last year’s winners. In 2020, DesignCon will add a new Best Paper category, recognizing an early-career engineer with less than seven years of professional experience.

Some of the DesignCon authors on the technical program committee will provide mentoring to early-career and first-time lead authors in an effort to make technical paper authorship a bit more accessible. This will be part of a special session on personal branding, which will also include members of the media and PR communities, sharing their expertise on how to share one’s knowledge with a broad audience.

You can catch up with the Signal Integrity Journal team at our booth T16 on the show floor, where we will be offering a chance to win an SI/PI library—yes of real, pick-them-up-and-feel-the-weight-of-them books. Stop by to take a look at the books, enter to win them, and take home some SIJ giveaways. We would also like to talk to you about how easy it is to publish your work in SIJ, and what you would like to see in future issues of the magazine.

Get 20% off a conference pass using promo code SIJ.

Here is the basic schedule for DesignCon 2020; looking forward to seeing you in January at the Santa Clara Convention Center!

Expo:

Wednesday, January 29: 11 a.m. – 6 p.m.

Thursday, January 30: 11 a.m. – 6 p.m.

Conference:

Tuesday, January 28: 9 a.m. – 6 p.m.

Wednesday, January 29: 8 a.m. – 5 p.m.

Thursday, January 30: 8 a.m. – 6 p.m.

Registration:

Tuesday, January 28: 7 a.m. – 5 p.m.

Wednesday, January 29: 7 a.m. – 6 p.m.

Thursday, January 30: 7 a.m. – 6 p.m.

Reference

1. J. Love, “DesignCon History: Looking Back 20 Years,” EDN Network, November 5, 2014.

Booth Previews

Cadence Booth #: 711

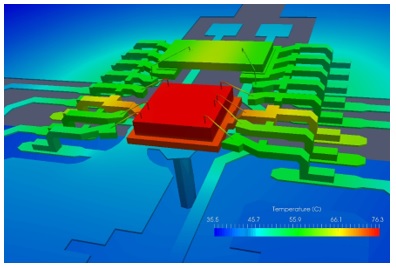

The Cadence booth will be buzzing with demonstrations from recent product announcements supporting Cadence’s Intelligent System Design™ strategy. The Cadence® Clarity™ 3D Solver and Celsius™ Thermal Solver deliver speed and capacity unseen in alternative solutions and based on a massively parallel architecture that is production proven in the Voltus™ IC Power Integrity Solution. Attendees will also be able to learn what’s new in Sigrity™ signal and power integrity technology. Simulations of advanced memory interface protocols and 128G serial link analysis are examples of leading-edge analysis capabilities being demonstrated.

Samtec Booth #737

Technology renaissances such as AI/HPC, 5G, and Auto 2.0 are driving new architectures that demand massive increases in transmission speeds, bandwidths, frequencies and densities. Samtec is presenting solutions to address these challenges, including 112 Gbps PAM4 interconnect systems, Artificial Intelligence and Machine Learning hardware, Direct Connect technology, and Samtec Flyover®. Samtec presentations include 112 Gbps on card edge (including QSFP-DD); PCie 32 G and 64 G; Current Distribution, Resistance and Inductance in Power Connector; Next Gen Materials; and validation and receiving 100 Gb/s signaling . Technology experts, cutting edge demonstrations, and the latest new product samples will all be available at booth 737. More information on demos and talks,

Sierra Circuits Booth #1148

GET ON BOARD with Sierra Circuits at this 2020 DesignCon! We’re embracing this new decade by putting the designer first with our brand new user-friendly website and our tools and services that assist you best. Rigid, flex, HDI, micro… Aerospace, military, automotive, medical… We just do it all. So come meet our PCB experts at booth #1148 and receive GET ON BOARD t-shirts and other goodies as well as free controlled impedance, HDI, flex and DFM design guides.

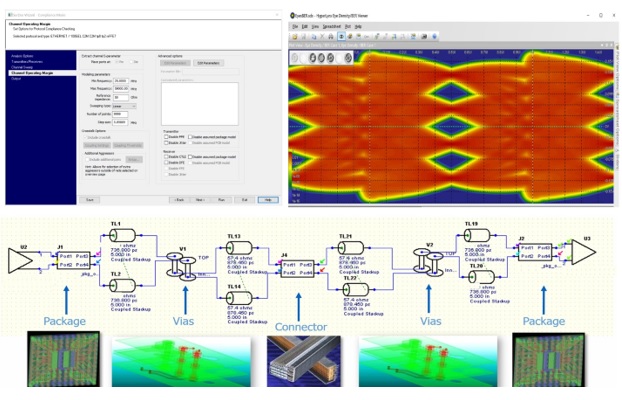

Mentor Booth #1043

Mentor®, a Siemens Business, will be demonstrating the complete HyperLynx® family of high-speed design tools including: electrical design rule checking, signal integrity, power integrity and integrated 3D electromagnetic modeling. HyperLynx automates design reviews to find issues early in the design cycle and provides complete analysis flows for DDRx, compliance-based SerDes channels and power delivery network (PDN) design. Mentor will also showcase new techniques for 112G SerDes channel compliance analysis, DDR5 design with IBIS-AMI models, automating PDN decoupling capacitor selection and board-level modeling of high-speed signals with complete return paths.

Anritsu Booth #837

Anritsu will demonstrate test solutions and techniques to verify high-speed communications. Among the industry-leading instruments on display will be the latest version of the broadband VectorStar™ VNA family targeting high frequency on-wafer applications, including device characterization. Also on display will be the Signal Quality Analyzer-R MP1900A series with a new PAM4 Error Detector (ED) supporting market-leading 116-Gb/s bit error rate tests. When combined with the previously released MP1900A series PAM4 Pattern Generator that supports high-accuracy BER measurements of PAM4 signals, the MP1900A can accurately evaluate bit error rates of 400 GbE/800 GbE communications equipment and devices.

Keysight Technologies Booth #725

Massive data flows from 5G and IoT are creating unprecedented demand for higher-speed digital throughput, interfaces, and memory in networks and data centers. At DesignCon 2020, Keysight will demonstrate its latest design and test solutions to enable customers to accelerate time-to-market of their latest high-speed interfaces, transceivers, and electronics. Featured demos include new DDR5 simulation and Rx/Tx test, 400GE PAM4 Tx test, 100 GBaud error analysis, and signal integrity/power integrity solutions. Highlighted products include Keysight’s 110 GHz UXR series and N1000A DCA-X Sampling Oscilloscopes, M8040A High-Performance BERT, and PathWave Design & Test Software. Learn more: https://www.keysight.com/us/en/events/america.html

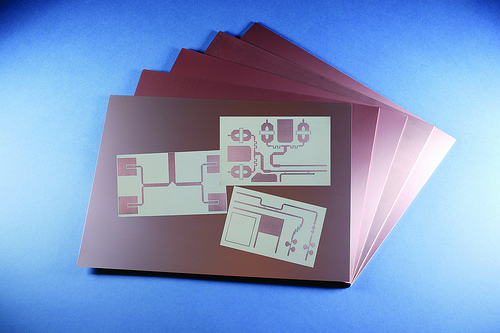

Rogers Corporation Booth #421

Rogers will highlight high performance circuit materials used in multilayer structures including a family of thin laminates and bonding materials.

This includes next generation products designed to meet the existing and emerging needs of advanced millimeter wave multilayer designs such as RO4835T™ low loss, spread glass reinforced, ceramic filled thermoset laminates, offered in a 2.5 mil, 3 mil and 4 mil core thickness, with a 3.3 Dk. These materials are designed for inner-layer use in multilayer board designs and they complement RO4835™ laminates when thinner cores are needed.

To complement the RO4835T and existing RO4000® laminates, RO4450T™ 3.2-3.3 Dk, low loss, spread glass reinforced, ceramic filled bonding materials come in 2.5, 3, 3.5, 4, 4.5, 5 or 6 mil thicknesses.

SiSoft and MathWorks Booth #935

Visit SiSoft and MathWorks and learn about exciting new developments in the areas of signal integrity, SerDes, and Mixed-Signal design. Don’t miss the opportunity to participate in the SerDes design and Mixed-Signal modeling challenges. Learn with practical examples how high-speed DDR5 and PAM4 interfaces have been designed using the integrated workflow between MATLAB® and Quantum-SI™ / Quantum Channel Designer® for channel simulation and IBIS-AMI modeling. In addition, understand how MATLAB® and Simulink® facilitate and speed up the design and verification of mixed-signal systems, such as PLLs, ADCs, DACs and more.

HUBER+SUHNER Booth #1145

Precision, reliability and repeatability are key characteristics for connectivity products in the test and measurement industry. New emerging applications such as 5G, automotive and semiconductor are continuously pushing the technological boundaries of interconnect test solutions in terms of speed, bandwidth, density and performance. HUBER+SUHNER will showcase its latest innovative solutions to meet the ever-changing technological challenges at the DesignCon 2020, 28-30 January, in Santa Clara. The new SUCOFLEX 570S, a 70 GHz high fidelity test assembly as well as the MXPM85 for state of the art multicoax measurements up to 85 GHz will be demoed this year at the HUBER+SUHNER booth.

Teledyne LeCroy Booth #513

Teledyne LeCroy will be exhibiting at DesignCon 2020 in booth 513. Stop by for live demonstrations and best measurement practices for PCI Express, USB, DisplayPort, power integrity and much more! Additionally, Teledyne LeCroy will be sponsoring a full day of seminar sessions open to all attendees in Mission City M3 on Thursday, January 30. For a full schedule, visit: http://teledynelecroy.com/designcon

Introspect Technology Booth #420

Introspect Technology, producer of extensible high-speed test and measurement equipment, will demonstrate its latest high-parallelism test and validation solutions. On display will be a live setup of our DDR5 test solution as well as our PCI Express Gen4 and Gen5 solutions. The DDR5 test solution is an ATE-on-a-Bench setup that can completely exercise and characterize a memory module or individual memory components supporting the next-generation JEDEC DDR5 standard. The PCI Express Gen4 and Gen5 demonstrations will illustrate link equalization measurement, loopback training, and receiver testing across multiple lanes simultaneously. Introspect Technology’s technical experts will be on hand to answer any questions about the DDR5 test solution and the PCI Express Gen4 and Gen5 solutions. They will also be available to offer knowledge and training on other topics ranging from MIPI to PAM4 and beyond. More information: www.introspect.ca

Carlisle Interconnect Technologies (CIT) Booth #514

Carlisle will showcase its CoreHCTM Ganged Interconnect System at Booth No. 514. CoreHC, a a multi-port system that offers innovative solutions to maintain signal integrity with the lowest losses across DC – 65 GHz in the industry.CIT representatives will be hosting two sessions at DesignCon 2020: Award-winning engineers Dave Correia and Raul Stavoli will host a boot camp session titled “Under the Hood: Understanding the Software that Drives Electromagnetic Simulation Tools,” Jan. 28 from 9 a.m. – 4:30 p.m. CIT Director of Engineering Emad Soubh and mechanical engineer Kelsey Fisher will host a technical session titled “Evolution of PCIe: Hardware Components & How they Impact Past, Present & Future Standards,” Jan. 29 from 2:50 – 3:30 p.m.

Ardent Concepts Booth #731

Ardent Concepts will have its products in the Amphenol booth, #731. In addition to Ardent Concepts’ 70 GHz+ TR Multicoax, SK Series Sockets, and CA Series Connectors, the booth will also feature new products including LinkOVER, which offers performance beyond 112G PAM4 per lane (demonstrated 100 Gbaud per lane), mates directly to PCB footprint symbol eliminating lossy paddlecard or male/female connector transitions, and comes in surface mount technology (SMT) or hardware mount. Ardent Concepts will also be showing its Right Angle 16-Channel TR Multicoax Connector, designed to alleviate height concerns in applications that are Z-height limited (7.62mm mated height). They will also show Host Compliance Test Fixture (HCTF), which is designed for 112G development and comes in QSFP-DD and OSFP form factors.