Mentor Graphics is gearing up for a strong presence at DesignCon 2017 (Santa Clara Convention Center, Santa Clara, CA; January 31-February 2). The company will host in-depth signal integrity training at its facility on January 31st, and will be building a theater style booth (#1043) on the show floor for continuous demonstrations on February 1 and 2. In addition, employee experts will be presenting three technical papers and will be receiving a Best Paper of the Year Award.

SI Bootcamp

Starting on Tuesday, January 31, Mentor Graphics will be hosting a “Practical, Hands-On Essential Principles of SI Bootcamp” from 8:30 until 4:00pm. If you attended his SI bootcamp at DesignCon 2016, you are already familiar with the presenter, Eric Bogatin (who is also the editor of the Signal Integrity Journal). Topics covered in this bootcamp include: transmission lines, stack ups, and signals; reflections, routing, and terminations; crosstalk; differential pair design and losses; loss and channels; and PDN design. The session will use simulation exercises in HyperLynx, so bring your laptop. This event requires pre-registration and is happening on the Mentor Graphics Fremont campus. You can register here.

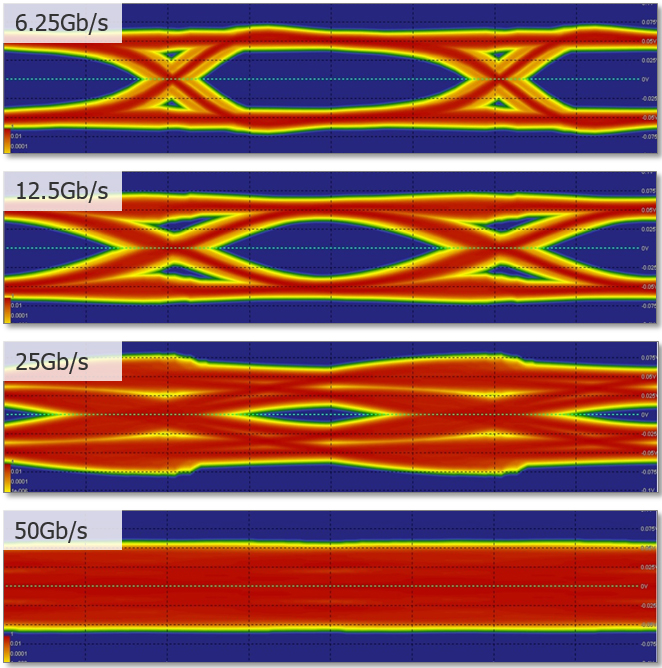

Figure 1: The effects on eye closure of increasingly high data rates on an actual SERDES channel are shown. Faster data rates/high frequencies demand more detailed simulation modeling.

Technical Papers

Employees from Mentor Graphics will be presenting three papers at this year’s DesignCon conference (technical sessions require a conference pass):

- Wednesday, February 1 at 11:00AM: "Optimization Methods for High-Speed SERDES Channels Using COM Metric;” Cristian Filip (Mentor Graphics), Daniel DeAraujo (Mentor Graphics), Michael Rowlands (Molex), and Priya Guruswamy (Univeristy of Colorado).

- Thursday, February 2 at 11:00AM: “Channel Operating Margin (COM) for PAM4 Links with Support for TX Non-Linearity and Time Skew;” Vladimir Dmitriev Zdorov (Mentor Graphics), Maria Agoston (Tektronix), and Pavel Zivny (Tektronix).

- Thursday, February 2 at 4:00PM: “SI Analysis of DDR BUS during Read/Write Operation Transitions;” Nitin Bhagwath (Mentor Graphics), Arapad Muranyi (Mentor Graphics), Randy Wolff (Micron), Atsushi Saito (Socionext), and Ikeda Sinichiro (Socionext).

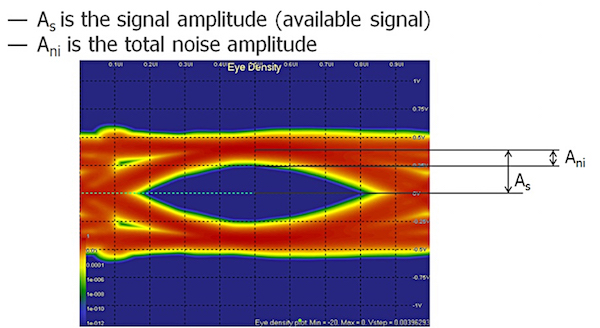

Figure 2: Channel Operating Margin (COM) allows checking the “goodness” of links based on a specific, complex set of simulation steps that in the end produces a single pass/fail number per-channel The new version of HyperLynx implements COM for 100GbE signaling, with all simulation details fully automated.

Booth Demos

On the show floor, in booth #1043, Mentor Graphics will be showcasing its HyperLynx simulation tools, specifically highlighting:

- HyperLynx Signal Integrity, which includes advanced tools for optimizing DDRx design, SERDES design projects, FastEye diagram analysis, S-parameter simulation, and BER prediction.

- HyperLynx Power Integrity, which allows users to model power distribution networks and noise propagation mechanisms throughout the PCB design process.

- HyperLynx DRC, which aims to accelerate electrical signoff with built-in rule-sets or customized rule checks for issues affecting EMI/EMC, signal integrity, and power integrity.

- HyperLynx Full-Wave Solver, a 3D, broadband, full-wave electromagnetic solver.

- Frontline InStack Design, an automatic stackup design tool to find the optimal stackup for your board,balancing between quality, manufacturability and price.

Finally, Mentor Graphics engineers Vladimir Dmitriev-Zdorov, Cristian Filip, and Chuck Ferry will share a DesignCon 2016 Best Paper Award with Al Neves from WildRiver Technology (and a Signal Integrity Journal Editorial Advisory Board member) for their paper “BER and COM Way Channel Compliance Evaluation: What are the Sources of Difference?”

See you at DesignCon! Signal Integrity Journal will be at tabletop T2. Use the promo code "INVITEME147" to save 15% off an All-Access or 2-Day pass, or claim a complimentary Expo Pass, at www.designcon.com/.