|

As rated by reader views, here are the Top 10 Articles on Signal Integrity Journal for 2017. Thank you for your readership in 2017, and we look forward to bringing you many more great technical features in 2018! |

|

|

|

|

|

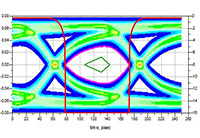

Ensuring High Signal Quality in PCIe Gen3 Channels By Anil Kumar Pandey The increased data rates of today’s high-speed Input/Output (I/O) buses make maintaining transmission channel signal quality all the more challenging. One reason for the challenge is the parasitic effects that result from bus interconnects. |

|

|

S-parameter Renormalization, The Art of Cheating By Gustavo J. Blando As you know, "us", Signal and Power Integrity Engineers, are full of tricks, rules of thumb, and shortcuts. These tricks mostly help us understand something, save analysis time and, why not, make us look smarter than we really are!! In that vein, seldom have I encountered a quick and dirty trick as useful and underestimated as S-parameter renormalization. |

|

|

S-parameters: Signal Integrity Analysis in the Blink of an Eye By Mike Resso, Keysight and Tim Wang Lee This article discusses new concepts for serial link design and analysis as applied to physical layer test and measurement techniques. Novel test fixtures and signal integrity software tools will be discussed in real world applications in the form of design case studies. |

|

|

Decoding the Smith Chart for Signal Integrity Engineers By Eric Bogatin Every RF engineer learns about the Smith Chart their first day studying S-parameters. It’s an important tool for RF applications. Not so for SI applications. But there are some valuable insights a Smith Chart can illuminate. Here’s how to extract those few nuggets. |

|

|

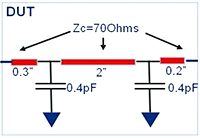

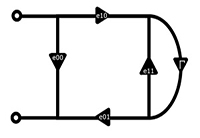

DC Blocking Capacitor Location, who cares? By Gustavo J. Blando It's a fact, the older I get, the dumber I become. I came to that realization while thinking about this eternal question engineers have about placement of high speed DC blocking caps in serial link channels. Read these insights about capacitor placement. |

|

|

By David Maliniak Double data-rate (DDR) memory has ruled the roost as the main system memory in PCs for a long time. Of late, it's seeing more usage in embedded systems as well. Let's look at the fundamentals of a DDR interface and then move into physical-layer testing. |

|

|

By Eric Bogatin Ground is NOT a current return path. Read on to see Todd Hubing’s four rules of effective grounding strategy. |

|

|

By Steve Sandler I’m not saying control loop stability isn’t important, of course it is. I am saying that whether your focus is power supply design, power integrity or mixed-signal, the Bode plot probably isn’t going to provide you with a reliable or optimum solution. Here are five major reasons for saying this... |

|

|

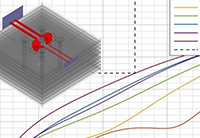

Better, Faster, More Confident 25+ Gbps Via Design: Applying Decomposition and Image Impedance By Ben Toby, Karl Bois Any discontinuity in a printed circuit board communication channel has the potential to significantly distort the signal propagating through it. This difficult-to-equalize distortion eats into loss budgets, ultimately reducing channel reach. |

|

|

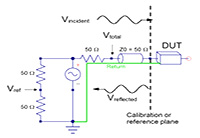

By Jason Ellison Typically, high-frequency VNAs measure interconnects and other RF devices on test fixtures. Test fixtures are something that signal integrity (SI) engineers need, but do not want. They are expensive, difficult to design, and cloud the performance of the device under test (DUT). De-embedding makes the murky waters between the SI engineer and the DUT clear by removing the fixture from the measurement. |